PX 2608

# CORE MEMORY Type 9150-10

Maintenance Manual

# RESTRICTED DISTRIBUTION

The information contained in this publication is the property of the Sperry Rand Corporation. It is submitted in confidence and must not be disclosed to others except in confidence with the written permission of an officer of the UNIVAC Division, Sperry Rand Corporation. This copy is not to be reproduced or duplicated without permission in writing from a duly authorized representative of the Sperry Rand Corporation. This publication is subject to recall.

Field Engineering Department llion, New York

# TABLE OF CONTENTS

| Pa | ragrap |                                                                                | Page                     |

|----|--------|--------------------------------------------------------------------------------|--------------------------|

|    |        | SECTION 1 - INTRODUCTION                                                       |                          |

|    | 1-1.   | GENERAL DESCRIPTION                                                            | 1-1                      |

|    | 1-2.   | FUNCTIONAL CHARACTERISTICS                                                     | 1-1                      |

|    | 1-3.   | PHYSICAL CHARACTERISTICS                                                       | 1-2                      |

|    | 1-4.   | INTERFACE CHARACTERISTICS                                                      | 1-2                      |

|    |        | CROWNEN D PUNCTIONAL PROGRAMMAN                                                | i ve                     |

|    |        | SECTION 2 - FUNCTIONAL DESCRIPTION                                             |                          |

|    | 2-1.   | SCOPE                                                                          | 2-1                      |

|    | 2-2.   | GENERAL                                                                        | 2-1                      |

|    | 2-3.   | CYCLES OF OPERATION                                                            | 2-1                      |

|    |        | a. Clear/Write Cycle                                                           | 2-2<br>2-2               |

|    | 2-4.   | MEMORY LOGICAL SECTIONS                                                        | 2-2                      |

|    |        | a. Timing and Control Section b. Address Section c. Unit Stack d. Data Section | 2-2<br>2-4<br>2-4<br>2-4 |

|    |        | SECTION 3 - LOGIC DESCRIPTION                                                  |                          |

|    | 3-1.   | GENERAL                                                                        | 3-1                      |

|    | 3-2.   | TIMING AND CONTROL SECTION                                                     | 3-1                      |

|    | 3-3.   | STORAGE LOCATION SELECTION                                                     | 3-2                      |

|    | 3-4.   | DATA SECTION                                                                   | 3-11                     |

|    | 3-5.   | CYCLES OF OPERATION                                                            | 3-15                     |

|    | . ••   | a. Clear/Write Cycle                                                           | 3-15<br>3-16             |

# TABLE OF CONTENTS (Cont.)

| Paragra | <u>ıph</u>                                                                                                                                          | Page              |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|         | SECTION 4 - CIRCUIT DESCRIPTION                                                                                                                     |                   |

| 4-1.    | GENERAL                                                                                                                                             | 4-1               |

| 4-2.    | COMPONENT IDENTIFICATION                                                                                                                            | 4-2               |

| 4-3.    | GENERAL CIRCUITS                                                                                                                                    | 4-3               |

|         | a. Inverter and AND Gate (Type AlO3) b. High Power Inverter (Type Al22) c. Low Power Inverter (Type Al23)                                           | 4-3<br>4-6<br>4-6 |

| 4-4.    | TIMING AND CONTROL CIRCUITS                                                                                                                         | 4-6               |

|         | a. Pulse Shaper-Delay Line Driver (Type A105) b. Delay Line Boards (Types A100, A120 and A121) c. Emitter Follower and AND Gate (Type A127)         | 4-6<br>4-8<br>4-9 |

| 4-5.    | ADDRESS SECTION CIRCUITS                                                                                                                            | 4-10              |

|         | <ul> <li>a. Selector Switch (Type A101) and Selector Switch Load (Type A102).</li> <li>b. Transformer-Diode Module (Type A118 and A119).</li> </ul> | 4-10<br>4-12      |

| 4-6.    | DRIVER CIRCUITS                                                                                                                                     | 4-13              |

|         | <ul><li>a. Read/Write Current Pulse (Generator)</li><li>b. Inhibit Driver (Type A107)</li></ul>                                                     | 4-13<br>4-17      |

| 4-7.    | AMPLIFIER CIRCUITS                                                                                                                                  | 4-21              |

|         | a. Preamplifier (Type A151) b. Sense Amplifier (Type A154) and Sense Amplifier Load                                                                 | 4-21              |

| 4-8.    | VOLTACE RECULATION CIRCUITS                                                                                                                         | 4-23              |

| • ••    |                                                                                                                                                     | 4-24              |

|         | Sink (Type Al17) Temperature Control (Type Al40)                                                                                                    | 4-24<br>4-26      |

|         | SECTION 5 - MAINTENANCE PROCEDURES                                                                                                                  |                   |

| 5-1.    | GENERAL                                                                                                                                             | 5-1               |

| 5-2.    | PREVENTIVE MAINTENANCE                                                                                                                              | 5-1               |

| 5-3.    | ROUTINE CHECKS                                                                                                                                      | 5-1               |

# TABLE OF CONTENTS (Cont.)

| Paragrap | e.<br><u>M</u> artin de la companya | <u>Page</u> |

|----------|-------------------------------------------------------------------------------------------------------------------------------|-------------|

| 5-4.     | TROUBLESHOOTING PROCEDURE                                                                                                     | 5-3         |

| 5-5.     | ADJUSTMENT PROCEDURE                                                                                                          | 5-3         |

| 5-6.     | MARGINAL CHECKING                                                                                                             | 5-3         |

|          | SECTION 6 - REMOVAL AND REPLACEMENT PROCEDURE                                                                                 |             |

|          | SECTION 7 - PARTS LIST                                                                                                        |             |

| 7-1.     | GENERAL                                                                                                                       | 7-1         |

| 7-2.     | FIGURE AND INDEX NUMBER                                                                                                       | 7-1         |

| 7-3.     | REFERENCE DESIGNATION COLUMN                                                                                                  | 7-1         |

| 7-4.     | UNIVAC PART NUMBER COLUMN                                                                                                     | 7-1         |

| 7-5.     | DESCRIPTION COLUMN                                                                                                            | 7-2         |

| 7-6.     | UNITS PER ASSEMBLY COLUMN                                                                                                     | 7-2         |

| 7-7.     | USABLE ON CODE COLUMN                                                                                                         | 7-2         |

# LIST OF ILLUSTRATIONS

| Figure |                                                                                                                                                                               | Page                 |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

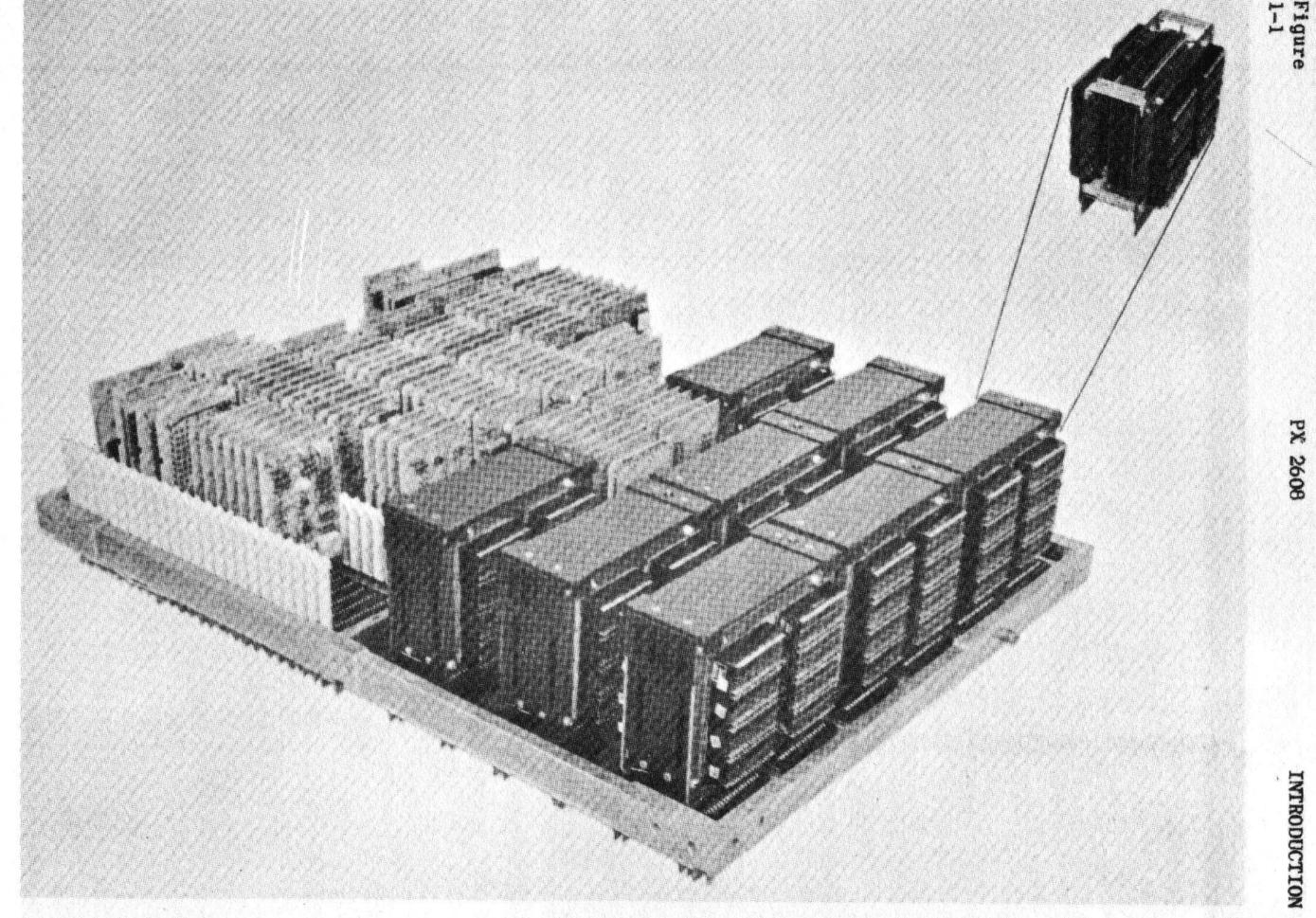

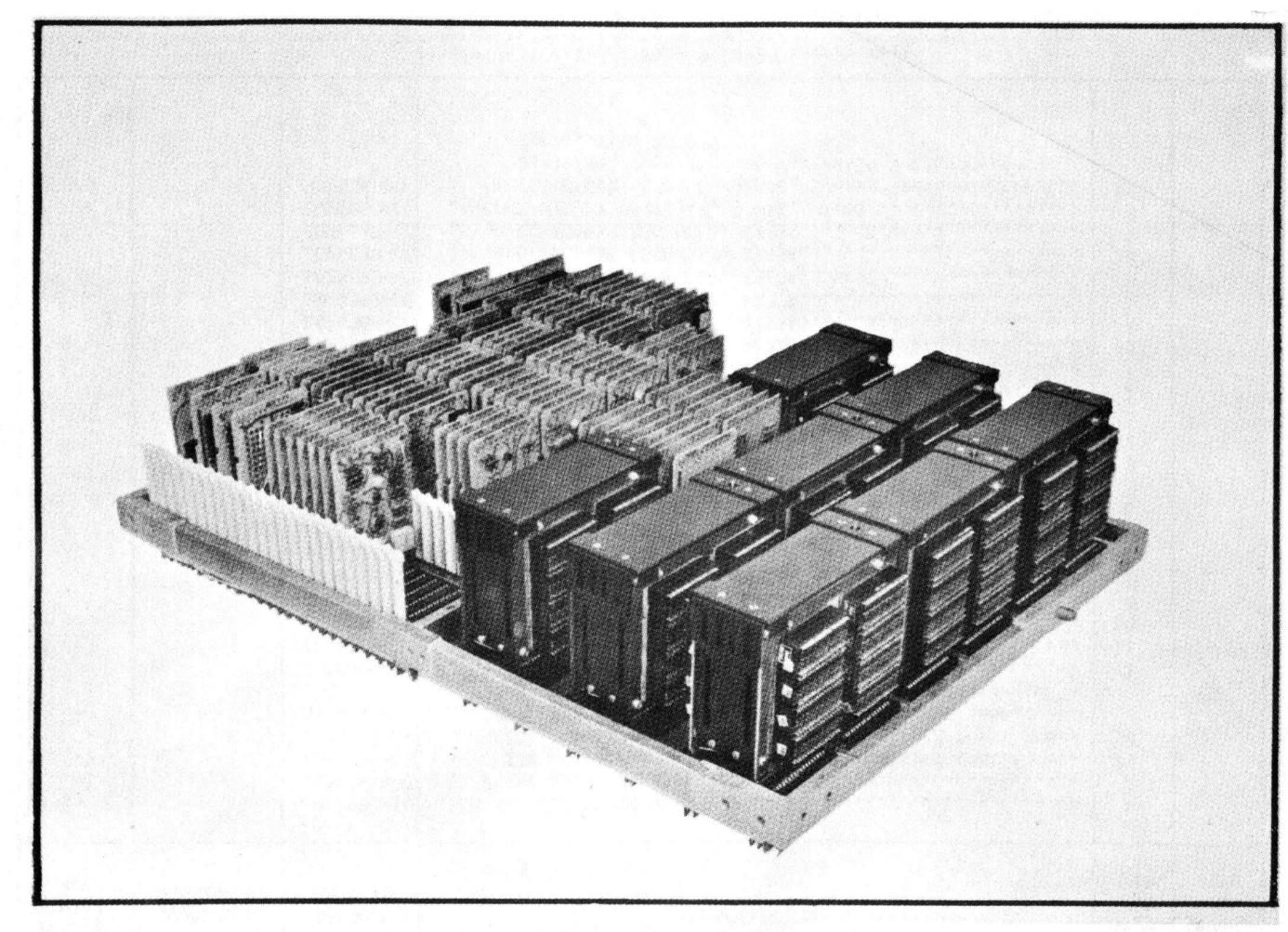

| 1-1.   | Type 9150-10 Core Memory for UNIVAC 1050                                                                                                                                      | 1-0                  |

| 2-1.   | 4K Memory Block Diagram                                                                                                                                                       | 2-3                  |

| 3-1.   | 32K Memory Block Diagram                                                                                                                                                      | 3-3                  |

| 3-2.   | Delay Line Timing Diagram                                                                                                                                                     | 3-5                  |

| 3-3.   | Timing Sequence of Clear/Write Cycle                                                                                                                                          | 3-7                  |

| 3-4.   | Timing Sequence of Read/Restore Cycle                                                                                                                                         | 3-9                  |

| 3-5.   | Selection Matrix Logical Representation                                                                                                                                       | 3-13                 |

| 4-1.   | Typical AND Gate Connection                                                                                                                                                   | 4-5                  |

| 4-2.   | Read Current Pulse Generation                                                                                                                                                 | 4-15                 |

| 4-3.   | <ul> <li>a. Voltage Regulator Output vs Temperature</li> <li>b. Read/Write and Inhibit Current vs +V Reg</li> <li>c. Read/Write and Inhibit Current vs Temperature</li> </ul> | 4-18<br>4-19<br>4-20 |

| 5-1.   | Rear View of Memory (Showing Voltage Terminals)                                                                                                                               | 5-2                  |

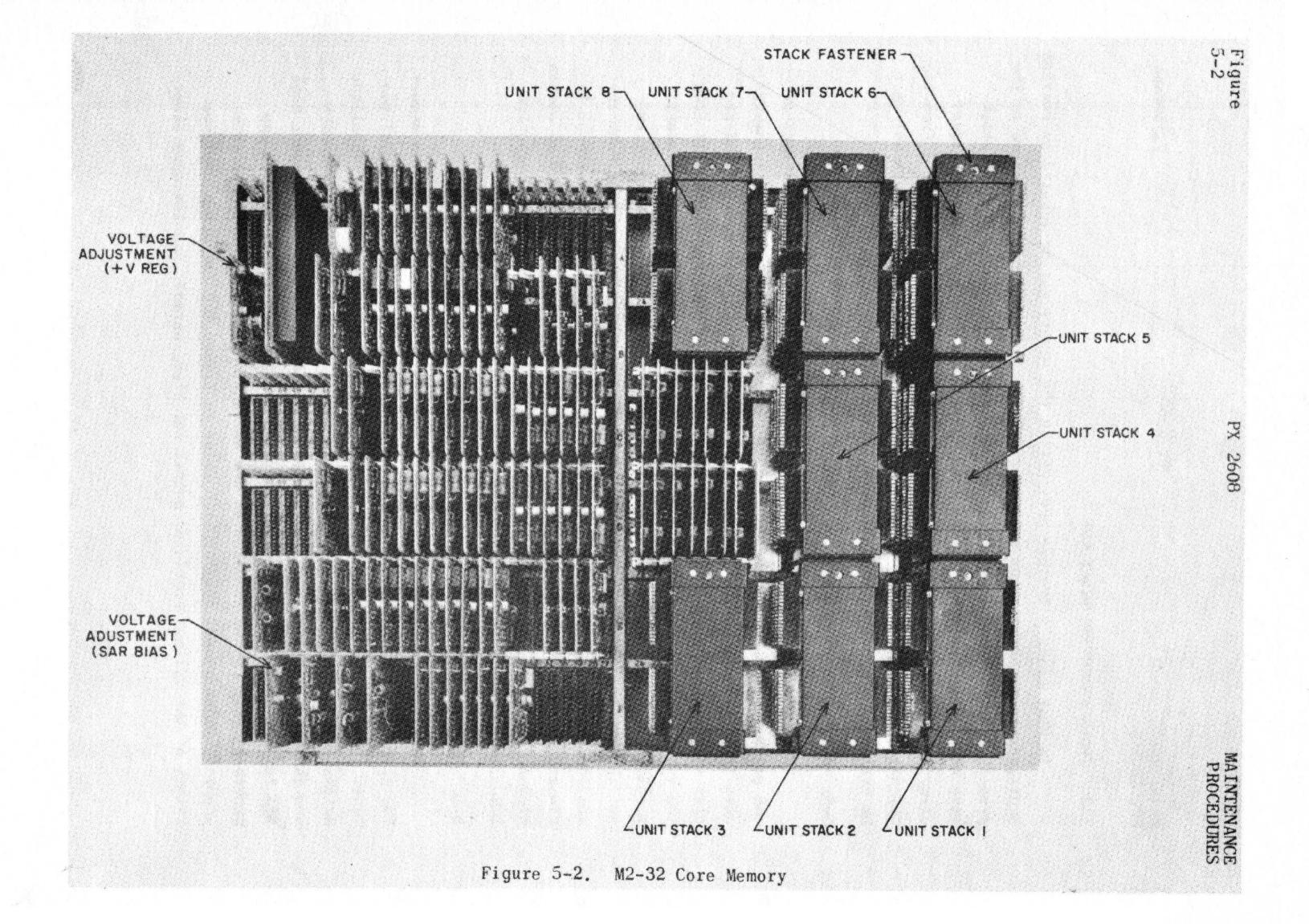

| 5-2.   | Type 9150-10 Core Memory                                                                                                                                                      | 5-4                  |

| 7-1.   | Type 9150-10 Memory Unit                                                                                                                                                      | 7-3                  |

| 7-2.   | Type 9150-9 Memory Unit                                                                                                                                                       | 7-5                  |

| 7-3.   | Type 9150-8 Memory Unit                                                                                                                                                       | 7-6                  |

| 7-4.   | Type 9150-7 Memory Unit                                                                                                                                                       | 7-7                  |

| 7-5.   | Type 9150-6 Memory Unit                                                                                                                                                       | 7-8                  |

| 7-6.   | Type 9150-5 Memory Unit                                                                                                                                                       | 7-9                  |

| 7-7.   | Type 9150-4 Memory Unit                                                                                                                                                       | 7-10                 |

| 7-8.   | Type 9150-3 Memory Unit                                                                                                                                                       | 7-11                 |

# LIST OF TABLES

| <u>Table</u> |                                 | Page |

|--------------|---------------------------------|------|

| 1-1.         | Interface Signals and Functions | 1-3  |

| 4-1.         | Printed Circuit Boards          | 4-1  |

| 4-2.         | Component Symbols               | 4-2  |

| 5-1.         | Voltage Checks                  | 5-1  |

| 5-2.         | Marginal Testing Procedures     | 5-5  |

Figure 1-1. Model M2-32 Core Memory From UNIVAC 1050

#### SECTION 1

#### INTRODUCTION

#### 1-1. GENERAL DESCRIPTION

The Type 9150-10 memory is a random-access, bit-organized, coincident-current core storage unit which can be readdressed every four and one-half microseconds. The memory together with the address and data registers of the processor provides data storage for the processor. The memory operates in either of two cycles, the clear/write cycle and the read/write cycle, which are controlled by signals received from the processor. During a clear phase of a clear/write cycle, the information stored in the memory at the selected address is read out and destroyed. New information from the processor is stored in the memory during the write phase. During a read phase of a read/write cycle, the information stored in the memory at the selected storage location is read out and transferred to the processor. Information from the processor is then restored in the original storage location during the write phase.

The memory is packaged on one UNIVAC standard 6 by 6 connector frame and is mounted in the processor cabinet. The electrical power and air cooling are provided by the processor power and cooling systems. The storage capacity of the type 9150-10 memory is variable in groups of 4096 characters from a minimum of 4096 seven-bit characters to a maximum of 32,768 seven-bit characters. The capacity is increased by plugging in the proper additional printed-circuit boards and unit stacks. The connector frame, connectors, and the backboard wiring for a maximum storage capacity memory are included in the minimum unit.

#### 1-2. FUNCTIONAL CHARACTERISTICS

Character bit length:

#### 7 bits

Storage Capacity: 9150-3 4,096 seven-bit characters

-4 8,192 seven-bit characters

-5 12,288 seven-bit characters

-6 16,384 seven-bit characters

-7 20,480 seven-bit characters

-8 24,576 seven-bit characters

-9 28,672 seven-bit characters

-10 32,768 seven-bit characters

Cycle Time:

4.5 microseconds

# 1-3. PHYSICAL CHARACTERISTICS

# Dimensions:

Width 26 1/2 inches Height 19 1/2 inches Depth 6 inches

#### Weight:

Minimum 45 pounds Maximum 60 pounds

#### Power Requirements:

| AC Voltage | None            |                 |

|------------|-----------------|-----------------|

| DC Voltage | Minimum Current | Maximum Current |

| +20 volts  | 8.0 amps        | 9.8 amps        |

| ground     |                 | •               |

| -8 volts   | 2.0 amps        | 5.2 amps        |

| -30 volts  | 2.5 amps        | 2.5 amps        |

# Cooling Requirements:

200 cfm

# 1-4. INTERFACE CHARACTERISTICS

The processor-memory interface signals and the function performed by each are listed in table 1-1. The polarity shown is when the signal is utilized.

TABLE 1-1. INTERFACE SIGNALS AND FUNCTIONS

| SIGNAL                                                   | LINE DESIGNATION                                                             | POLARITY | FUNCTION                                                                                          |

|----------------------------------------------------------|------------------------------------------------------------------------------|----------|---------------------------------------------------------------------------------------------------|

| Input Signals<br>Unit Stack Select                       | PARU1<br>through<br>PARU8                                                    | +        | Selects corresponding stack by selecting the associated read/write diverters and inhibit drivers. |

| Timing Pulse                                             | PTP2M                                                                        | <u> </u> | Initiates internal memory timing                                                                  |

| Unit Enable                                              | PBUEA                                                                        | +        | Enable read/write current generators                                                              |

| Read Enable                                              | PREAD                                                                        | +        | Enable the strobe gate.                                                                           |

| Address<br>Information                                   | PARYO through                                                                | +        | Provides Y-axis line selection                                                                    |

|                                                          | PARXO through                                                                | +        | Provides X-axis line selection                                                                    |

|                                                          | PARY00<br>PARY10<br>PARY20<br>PARY30<br>PARY40<br>PARY50<br>PARY60<br>PARY70 | +        | Provides X-axis bus<br>selection                                                                  |

|                                                          | PARXOO through                                                               | +        | Provides X-axis bus selection                                                                     |

| Write Data                                               | PMZ1 through                                                                 | + for 0  | Data to be stored in memory                                                                       |

| Output Signals<br>Output Data                            | MOZO1 through<br>MOZO7                                                       | + for 0  | Data read from memory and transferred to the processor                                            |

| Marginal Check<br>Voltage Lines<br>Marginal Check<br>Low | OZMCM2                                                                       |          | Controls the output from the Read/Write and inhibit                                               |

| Marginal Check<br>High                                   | OZMCM1                                                                       | -        | drivers by controlling the voltage regulator output.                                              |

|                                                          |                                                                              |          |                                                                                                   |

|                                                          |                                                                              |          |                                                                                                   |

#### SECTION 2

#### FUNCTIONAL DESCRIPTION

#### 2-1. SCOPE

This section describes the functional operation of the logical sections of the memory. A detailed logic description is presented in Section  $\bf 3$ .

#### 2-2. GENERAL

The type 9150-10 memory provides data storage for the processor. When utilizing the memory, the processor may either store data in the memory or retrieve data from the memory, depending on the requirements of the given processor operation. When data is to be stored in memory, the memory performs a clear/write cycle of operation and, when data is to be retrieved from the memory, a read/write cycle of operation is performed. When performing either cycle of operation, the memory is dependent upon the processor for control information pulses.

#### 2-3. CYCLES OF OPERATION

The operation of the memory cycles must coincide with the processor timing sequence. Thus the processor initiates the memory action and also provides the memory with the input data at the proper time. Since the processor is the controlling agent, the cycle in which the memory operates is determined by the processor. Also the storage location and the core stack to be utilized are selected by signals from the processor. The transfer of information from the memory to the processor and the step-by-step timing of a memory cycle are controlled by the memory timing circuits.

During memory operation the initiating pulses (PTP2M and PBUEA), the address information (PARX-, PARX--, PARY-, and PARY--), one of eight unit stack select signals ( $\overline{PARU1}$  through  $\overline{PARU8}$ ), and the read enable ( $\overline{PREAD}$ ) which controls the cycle of memory operation are sent to memory by the processor. (When the read enable is sent to the memory, a read/write cycle is initiated. When the read enable is not sent to the memory, a clear/write cycle is initiated.) At this point the timing and control section of the memory assumes control,

and utilizing the signals received from the processor, a unit stack and the storage location within the stack are selected. Then either a clear/write cycle or a read/write cycle is performed.

a. CLEAR/WRITE CYCLE. - During the clear phase of the clear/write cycle the data stored at the selected storage location is read from the cores. Because the read enable is not received from the processor during this phase, the strobe pulse is not developed and the data read from the cores is not transferred to the processor, but is destroyed.

During the write phase, the processor sends new data to the memory. This new data is stored or written in the same storage location from which the old data was read out and destroyed.

b. READ/WRITE CYCLE. - During the read phase of the read/write cycle, the data stored at the selected storage location is read from the cores. The read enable pulse and a timing pulse from the memory timing circuits provide a strobe pulse which transfers the amplified version of the data read from the cores to the processor.

During the write phase, the processor sends data to the memory. This data is then stored in the same storage location from which the original data was read.

#### 2-4. MEMORY LOGICAL SECTIONS

The following paragraphs describe the functional operation of the logical sections of the memory. Figure 2-1 is a block diagram of a 4K memory showing the interrelations among the timing and control section, the address section, the core stack, and the data section.

a. TIMING AND CONTROL SECTION. - This section contains the internal timing circuits and the control circuits operated from the timing circuits. The timing circuits receive the PTP2M pulse from the processor which initiates the timing action of the memory. The timing pulses from the timing circuits are used in conjunction with the unit enable and read enable signals from the processor to operate the control circuits. The control circuits provide the necessary pulses for internal timing and control of the memory.

- b. ADDRESS SECTION. This section contains the selector switches, the X and Y selection systems and the X and Y read/write current generators. The selector switches are operated by the address information from the processor and control the X and Y selection systems. The selection systems select one X drive line and one Y drive line in each stack and provide a path to supply the driving currents to the selected drive lines. The read/write current generators supply the current necessary to switch the selected cores.

- c. UNIT STACK. A unit stack consists of seven core planes. One storage location (a core in each plane) is selected when one X drive line and one Y drive line are selected by the selection system. Information received from the processor is stored in the core stack.

One of the eight unit stacks is selected by the unit stack select pulse which enables the associated read/write diverters and inhibit drivers.

d. DATA SECTION. - This section contains the preamplifiers, the sense amplifiers, and the inhibit drivers. The preamplifiers receive the signals read from the core stack, amplify them, and reduce the noise pulses to a level below the saturation level of the sense amplifiers. Each sense amplifier receives the outputs from a maximum of eight preamplifiers, only one of which is active during a given cycle, and amplifies the signal; when strobed, the amplifier outputs are transferred to the processor. The inhibit drivers are selected by the unit stack signals and are timed by the inhibit driver enable timing pulse from the timing and control section; when O data bits are received from the processor, the drivers supply the inhibit current to the core stack. The inhibit current counteracts the effect of the Y write current during a write phase and prevents writing a l in that plane.

#### SECTION 3

#### LOGIC DESCRIPTION

#### 3-1. GENERAL

This section explains the logical operation of the memory. Paragraphs 3-2 through 3-4 describe the operation of logic sections outlined in Section 2. The interactions of the logic sections are demonstrated in descriptions of the clear/write cycle and the read/write cycle under paragraphs 3-6 and 3-7.

The logic of the memory is presented on drawings 4026120 through 4026123, 4026125, 4026126, 4026142, 4026144, 4026146 and 4026147. Figure 3-1 is a block diagram of a 32,768-character memory. The circuits represented by the blocks enclosed within the dashed lines must be added to increase the memory capacity from 4096 characters. All other circuits represented are common to all capacity options.

#### 3-2. TIMING AND CONTROL SECTION

This section contains a 4.0-microsecond delay line, the delay line drivers, and the control circuits operated from the delay line. The timing and control section receives the PTP2M pulse, the unit enable (PBUEA) and the read enable (PREAD) signals from the processor and develops the internal timing and control pulses for the memory. The timing and control pulses developed are the read driver enable (RDRVRE), the read diverter enable (RDVTRE), the strobe pulse, the write driver enable (WDRVRE), the write diverter enable (WDVTRE) and the inhibit driver enables 1 through 4 (IDE 1).

Drawing 4026120 is the logic diagram of the timing and control section. The delay line has taps available at 50-nanosecond increments. A pulse is applied to the input of the delay line; as it traverses the delay line, it is tapped off at the required time to control the timing of the memory. Figure 3-2 is a timing diagram of the pulse tapped from the delay line. Drawing 4026154 is a timing diagram of key memory signals. The times shown on the diagram are typical and may vary from one memory to the next. The use of these pulses may best be understood by referring to figures 3-3 and 3-4. These figures show the timing sequence for a clear/write cycle and a read/write cycle.

The pulse applied to the delay line is developed from timing pulse, PTP2M, received from the processor. PTP2M sets the single-shot multivibrator. The inverter in the 1 output line from the SS sends a negative going pulse to the 0.4-microsecond time delay circuit. Since the time delay circuit is an open ended delay line, the input pulse is reflected back. The time required for the pulse to traverse the delay circuit and to be reflected back is 0.8 microsecond. Thus, a 0.8-microsecond negative pulse is developed and applied to the 4.0-microsecond delay line circuit which supplies the internal timing of the memory. The first timing pulse from the 4.0-microsecond delay line clears the single-shot multivibrator. The SS stays in the clear state until the PTP2M pulse is received at the beginning of the next cycle.

#### 3-3. STORAGE LOCATION SELECTION

This section is composed of the selector switches, the X and Y transformer diode matrices, and the X and Y read/write current generators. The selector switches receive the address information from the processor and control the X and Y transformer diode matrices. The matrices each select one drive line and provide a path to supply the driving currents to the cores. The read/write current generators supply the driving current necessary to switch the selected cores.

The logic diagrams of the selection section are 4026121, 4026126, 4026142 and 4026144. Address information is received from the processor in octal code. Thirty-two bits, divided into four groups of eight bits each, are required for the X and Y selection. Address bits PARXO through PARXT operate the X line switches, bits PARXOO through PARXOT operate the X bus switches, bits PARYOO through PARXOT operate the X bus switches, bits PARYOO, PARYOO

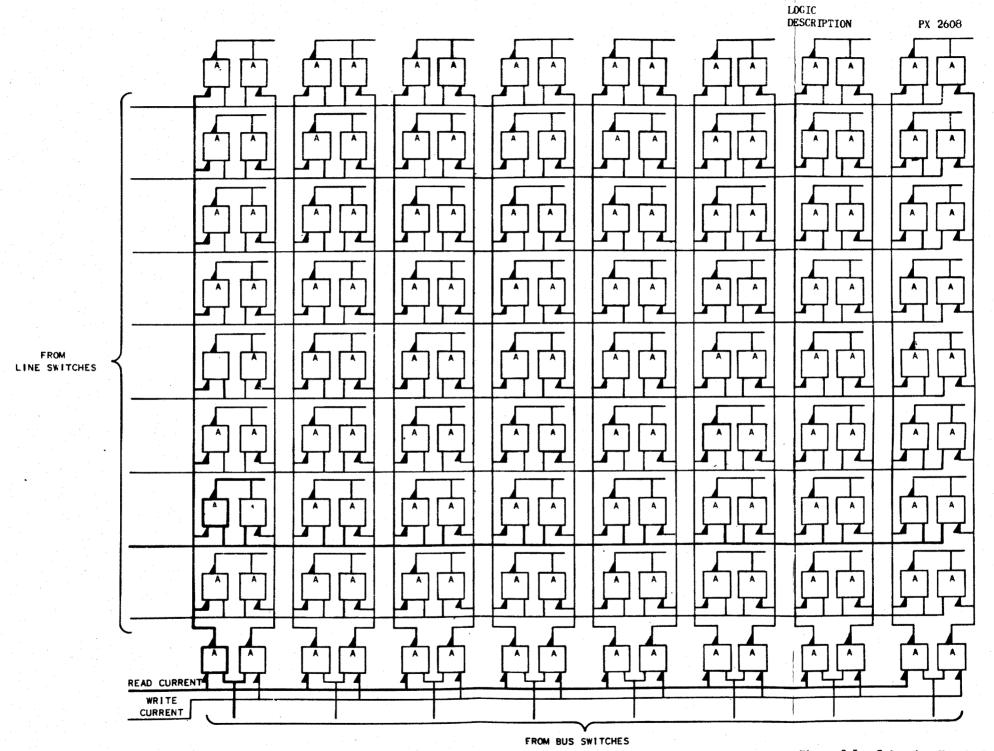

The selection of one line switch and one bus switch by the address information provides a path for the application of the driving current to the core stack drive line. The actual selection of a drive line is not completed

LOGIC

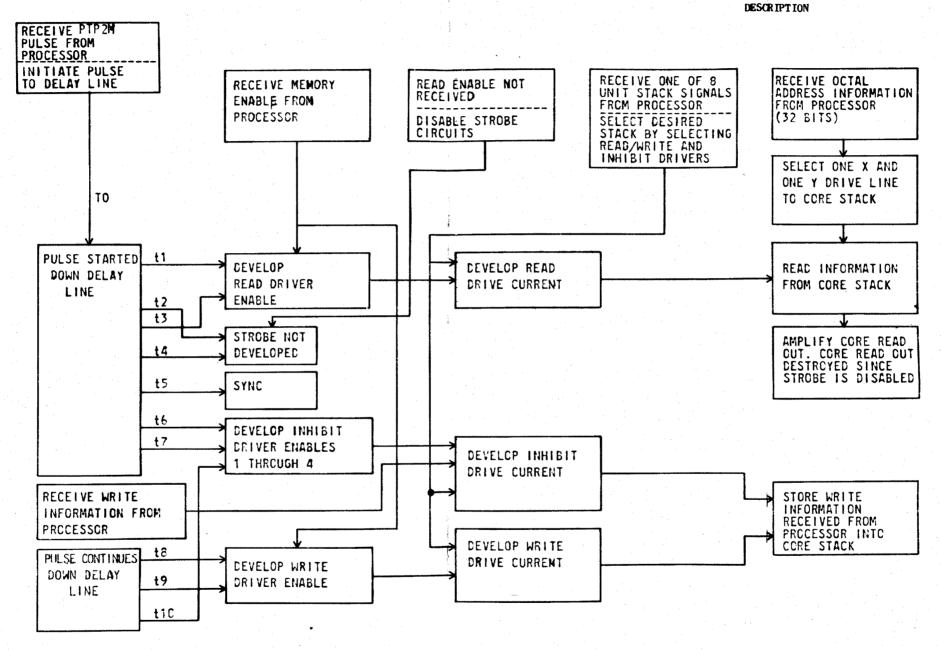

Figure 3-3. Timing Sequence of Clear/Write Cycle

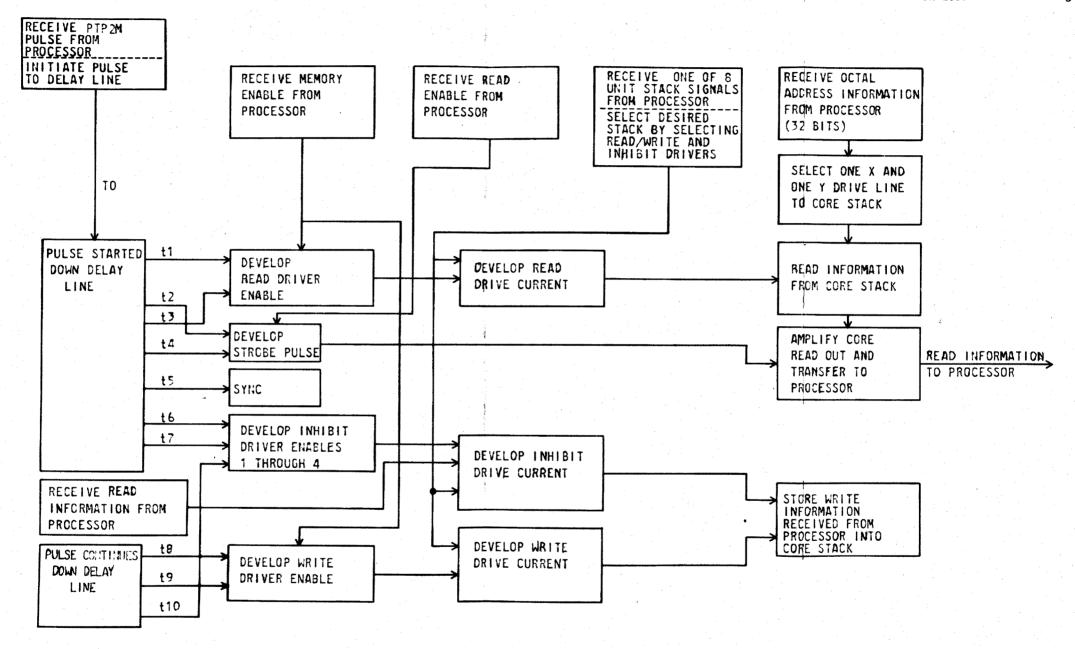

Figure 3-4. Timing Sequence of Read/Restore Cycle

until the read or write drive current is supplied to the selection system bus transformers. The read current generator for the addressed stack is selected by the unit stack select pulses USS1 through USS8, and when the read driver enable is received from the timing section of the memory, the generator is operated and supplies driving current to the selection system bus transformer. The read drive current is transformer coupled to the selected core stack drive line by the selected line transformer. The selection of one output from the selection system and the flow of read current is shown by heavy lines on figure 3-5. The flow of write current is identical to that of the read current utilizing the opposite half of the bus and line transformers. The write drive current is supplied by the write current generator which is selected by the unit stack pulse and timed by the write driver enables from the timing section of the memory.

#### 3-4. DATA SECTION

This section is composed of 56 preamplifiers, 7 sense amplifiers, and 56 inhibit drivers for a full capacity memory. A full capacity memory is the type 9150-10 consisting of eight unit stacks of seven planes each and the associated electronic circuits. The sense output from each plane is connected to a preamplifier, thus the requirement for the 56 preamplifiers. The outputs from the preamplifiers associated with the same plane in each of the eight unit stacks are OR gated together and supply the input to one sense amplifier. Thus only seven sense amplifiers are required. This OR function is possible since only one of the eight preamplifiers is active during any one cycle. The interconnection of eight preamplifiers to one sense amplifier is shown on logic diagram 4026125.

The preamplifier receives the core readout from the sense line, amplifies the signal, and transfers it to the sense amplifier. The sense amplifier amplifies both the 1 and the 0 signals read from a core; however, the level of the 0 signal is small compared to that of the 1. Thus, by strobing the output from the sense amplifier at a level above the 0 signal and timed for the 1 signal a distinction is made between the two signals. The presence of a signal on the output data lines indicates that a 1 was read from the core, and the absence of a signal on the output data lines indicates that a 0 was read from the cores.

The above explanation is true only for the read phase of the read/write cycle. During the clear phase of a clear/write cycle the data stored in the core stack is read out and goes through the preamplifiers and sense amplifiers; however, the output from the sense amplifier is not strobed to the processor. Thus the readout from the unit stack is destroyed during the clear phase.

The inhibit drivers receive the input data from the processor during a write phase and develop inhibit current in the selected stack (logic drawings 4026122 and 4026123). The input to the drivers is a three-input AND gate. Thus the unit stack select signal, the inhibit driver enable, and a O input pulse is required to operate the individual driver. The PARU pulse is received from the processor and enables the inhibit drivers associated with only one stack during any one cycle. The inhibit driver enable is received from the memory timing and control section and enables all inhibit drivers in the memory. The input data is received from the processor by all inhibit drivers; however, the only drivers that operate are those that receive the USS signal.

The logic diagrams of the data section are 4026122, 4026123, and 4026125. To increase the capacity of the memory, unit stacks, preamplifiers, inhibit drivers, and stack select circuits are added. The sense amplifiers are capable of handling up to eight preamplifier outputs each. Thus only seven sense amplifiers are required for any capacity option. When less than eight stacks are used, load impedance is added to the input of the sense amplifiers to maintain the impedance match between the sense amplifiers and the preamplifiers.

During a read phase the information stored in the core stack is read out and transferred to the preamplifiers. The preamplifiers amplify the readout, eliminate the common mode noise pulses, and limit the bipolar noise pulses. The output from the preamplifiers is transferred to the sense amplifiers, which amplify the signal and transfer it to the processor during strobing. During a clear phase, the data stored in the core stack is read out and goes through the preamplifiers and sense amplifiers, but it is not strobed to the processor. Thus, the readout from the core stack is destroyed during the clear pulse.

During a write phase, data is received from the processor by the inhibit drivers. The input data from the processor along with the inhibit driver

Figure 3-5. Selection Matrix Logical Representation

enable and the unit stack signal operate the inhibit drivers. The inhibit drivers that receive 1's from the processor are disabled while the drivers that receive 0's from the processor are operated. The cores in the stack that receive both the write current and the inhibit current store 0's. The cores in the stack that receive only the write current store 1's.

#### 3-5. CYCLES OF OPERATION

The memory will perform either a clear/write cycle or a read/write cycle, depending upon the signal received from the processor. The PTP2M pulse starts the timing action of the memory. The unit enable (PBUEA) signal enables the read/write current generators. If the read enable (PREAD) signal which enables the strobe circuit is received from the processor, a read/write cycle is initiated. If the read enable signal is not received from the processor, the strobe circuits are disabled, and a clear/write cycle is initiated.

a. CLEAR/WRITE CYCLE. - When the memory receives the PTP2M pulse and the PBUEA signals from the processor, a clear/write cycle is initiated. From the PTP2M pulse, the memory develops the timing pulse and applies it to the delay line. The timing pulse is tapped from the delay line at times tl throug tl3 and controls the timing of the memory circuits.

The PBUEA is received from the processor. It is AND gated with timing pulses t2 and t4 to develop the read drive enable pulse and the read diverter enable pulse. However, the latter pulse enables all read diverters in the memory. The only diverter that operates is the one selected by the unit stack signal from the processor. If information is to be stored in unit stack 1, the unit stack 1 signal is received from the processor. The read driver enable pulse operates the read driver. The octal address information is received and the storage location is selected by the selector switches operating the X and Y selection matrices of all stacks. Since only one read diverter is operated by the unit stack signal, only the information stored in that stack is read out and applied to the preamplifiers associated with that stack. The output from the preamplifiers is applied to the sense amplifiers where the readout from the core stack is amplified and rectified. Since the strobe pulse is not developed during a clear/write cycle, the information read from the cores is destroyed.

Timing pulses t8, t9, and t13 are OR gated together and develop the inhibit driver enable (IDE) pulses 1 through 4. IDE 1 enables the inhibit drivers for stacks 1 and 2. IDE 2 enables the inhibit drivers for stacks 3 and 4. IDE 3 enables the inhibit drivers for stacks 5 and 6 while IDE 4 enables the drivers for stacks 7 and 8. As in the case of the read diverters, only the inhibit drivers that receive the unit stack signal from the processor are alerted. The write data is received from the processor and applied to the inhibit drivers. The inhibit drivers associated with the selected stack operate; i.e., the inhibit drivers that receive 0 information from the processor provide inhibiting current to the selected plane, but the inhibit drivers that receive 1 information from the processor do not supply inhibit current.

Timing pulses t10 and t12 are AND gated with the memory enable signal to start the write drivers, which supply drive current to the diverters selected by the unit stack signal. This supplies the write driving current to the selected core stack. The selected cores within the stack that receives both the inhibit current and the write current store 0's. The cores that receive only the write current store 1's. Timing pulse t13 keeps the inhibit drivers on until after the write drivers have been turned off. This prevents writing 1's in all the selected cores.

b. READ/WRITE CYCLE. - The read/write cycle is similar in operation to the clear/write cycle. The only differences are that the read enable is received from the processor and the strobe pulse is developed. The strobe pulse enables the transfer of the data read from the core stack to the processor. The remainder of the cycle is identical to the clear/write cycle.

#### SECTION 4

#### CIRCUIT DESCRIPTION

#### 4-1. GENERAL

This section presents the theory of operation of the electronic circuits used within the Type 9150-10 memory. The circuits are divided into six categories according to their functional use within the memory (refer to table 4-1). In some cases an electronic circuit is packaged on more than one printed circuit board because of the physical limitations of the board. In these cases, a composite schematic of the circuit is presented in this section. The schematics for the circuits packaged on one printed circuit board, may be found in the machine documentation manual. With the exception of the transformer-diode module, all schematics are on the assembly drawings. The assembly drawing numbers are listed in table 4-1.

TABLE 4-1. PRINTED CIRCUIT BOARDS

| TYPE<br>NO. | TITLE                          | ASSEMBLY<br>DWG. NO. | ABBR.              |

|-------------|--------------------------------|----------------------|--------------------|

|             | CEATERAL GARGIATEC             |                      | •                  |

| 4100        | GENERAL CIRCUITS               |                      |                    |

| A103        | Inverter and AND Gate          | 4026309              | N, A               |

| A122        | High Power Inverter            | 4026362              | HGN                |

| A123        | Low Power Inverter             | 4026365              | HGN                |

|             | TIMING AND CONTROL CIRCUITS    |                      |                    |

| A105        | Pulse Shaper-Delay Line Driver | 4026315              | SS. N. TD4         |

| A100        | Delay Line                     | 4026300              | DL                 |

| A120        | Delay Line                     | 4026360              | DL                 |

| A121        | Delay Line                     | 4026361              | DL                 |

| A127        | Emitter Follower; AND Gate     | 4026377              | EF, A              |

| · · ·       | ADDRESS SELECTION CIRCUITS     |                      |                    |

| A101        | Selector Switch                | 4026303              | AR                 |

| A102        | Selector Switch Load           | 4026306              | XBL, YBL, XLL, YLL |

| A118-A119   | Transformer-diode Modules      | 4026354              | A                  |

|             | DRIVER CIRCUITS                |                      |                    |

| A113        | Read/Write Driver              | 4026339              | RDRV R. WDRV R     |

| A114        | Read/Write Diverter            | 4026342              | RDVTR, WDVTR       |

| A115        | Power Resistor                 | 4026345              | DRVRL1, DRVRL2     |

| A107        | Inhibit Driver                 | 4026321              | N.ID               |

| TYPE<br>NO. | TITLE                       | ASSEMBLY<br>DWG. NO. | ABBR. |

|-------------|-----------------------------|----------------------|-------|

|             | AMPLIFIER CIRCUITS          |                      |       |

| A151        | Preamplifier                | 4026437              | PAR   |

| A154        | Sense Amplifier             | 4026204              | SAR   |

| A133        | Sense Load Card             | 4026399              | SARL  |

|             | VOLTAGE REGULATION CIRCUITS |                      |       |

| A116        | Voltage Regulator           | 4026348              | l VR  |

| Al 17       | Voltage Regulator Heat Sink | 4026351              | VRHS  |

| A140        | Temperature Control         | 4026420              | R     |

| A153        | Sense Bias Regulator        | 4026442              | VR    |

TABLE 4-1. PRINTED CIRCUIT BOARDS (Cont.)

# 4-2. COMPONENT IDENTIFICATION

The grid system of component placement is used on all printed circuit boards. (Refer to drawing 4026300.) Therefore, all components on the schematic diagram are identified by the grid location where the topmost or leftmost component lead connects to the board. The standard symbol such as R for resistor is not included on the schematic. For ease in identifying the components when referred to in the text, the standard symbols listed in table 4-2 are used along with the grid reference of the component connections. Thus the text reference for a resistor that has its topmost or leftmost lead wire connected to the board at L3 would appear as follows:

R(L3)

When referencing a transistor, only the collector lead connection is identified.

TABLE 4-2. COMPONENT SYMBOLS

| Symbol                      | Component                                                       |

|-----------------------------|-----------------------------------------------------------------|

| C<br>CR<br>L<br>Q<br>R<br>S | Capacitor Diode Inductor Transistor Resistor Switch Transformer |

#### 4-3. GENERAL CIRCUITS

a. INVERTER and AND GATE (TYPE A 103), ASSEMBLY DWG, NO. 4026309

# Circuits per Board: 6

| major Component    |

|--------------------|

| Q(Q6)              |

| Q(L7)              |

| Q(G7)              |

| Q(C7)              |

| CR(T1) and CR(U2)  |

| CR(T5) and CR(T12) |

|                    |

#### Current Ratings:

| Low Power | Inverter    | High Power | Invert  | er   |

|-----------|-------------|------------|---------|------|

| 6.42 ma   |             | 20.6 ma    |         |      |

|           | -0.275 volt | 100.0 ma   | -0. 285 | volt |

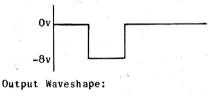

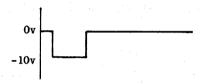

## Waveshapes:

Input Waveshape:

Input Current:

Output Current:

(1) CIRCUIT FUNCTION. - The inverters provide inversion and current gain for the timing control of the memory and for the interface signals. The inverters used in the timing control section supply the current necessary to operate the read/write drivers, the inhibit drivers, and the strobe circuit. The interface inverters drive the stack selection circuits and provide inversion for the read enable signal. Each inverter has a diode input and one direct input, only one of which may be used in a given instance. The diode input is used when isolation between the signal source and the inverter is required.

The AND gates consist of two diodes with separate inputs and a common output. The input and output pins which are available at the backboard are used throughout the system where AND gate logic is required.

power inverters is identical. For the following explanation refer to circuit 1 transistor Q(Q6) of the schematic diagram listed at the heading of this section. When a high signal (0 volt) is presented to either input of the inverter, the base of the inverter transistor is driven positive from the +20 volt source due to the voltage divider action of resistor R(10) and diode CR(R10). This positive potential reverse-biases the emitter-base junction of the transistor and prevents conduction. In this state the output from the transistor is low (-8 volts). When a low signal is presented to either input of the inverter, the base of the inverter transistor is driven negative from the +20 volt and -30 volt sources by the voltage divider action of resistors R(S3), R(S7), and R(Q10). The negative potential, at the base of the transistor, forward-biases the emitter-base junction and the transistor conducts. In this state the transistor output is high (0 volt) and a low impedance path to ground through the collector-emitter of the transistor is presented to the output circuit.

The switching time of the transistor and thus the rise and fall time of the output signal is decreased by capacitor C(R1) in the base circuit. During turn-on of the transistor, the capacitor provides a path for the transient currents to enter the base circuit, and forward-bias the emitter-base junction. During turn-off the capacitor discharges through the emitter-base junction applying a reverse-bias potential to the transistor.

The AND gates shown on the assembly drawing consist of diodes and interconnecting printed circuitry. The voltage and current sources necessary for operation must be supplied by the circuits connected to the inputs and output. Figure 4-1 is a schematic of the AND gate and typical input output circuits. If either input to the AND gate is at 0 volt, the associated diode conducts and the output from the gate is nearly 0 volt which reverse biases the second diode, preventing its conduction.

When both inputs to the AND gate go negative, as shown in figure 4-1, the voltage divider network consisting of R3, R4, and R5 applies approximately -6 volts to the AND gate output. Since this potential is more positive than the

Figure 4-1. Typical "AND" Gate Connection

input potential to the AND gate, the diodes are reverse biased and do not conduct. In effect, no output exists from the AND gate and the inverter transistor is free to conduct.

b. HIGH POWER INVERTER (TYPE A122) ASSEMBLY DWG. NO. 4026362

Circuits per board: 4 identical

Current Ratings:

Input Current:

20.6 ma

Output Current

$-0.285 \pm 0.135$  volts 100 ma

- (1) CIRCUIT FUNCTION. The inverters on this board are used in conjunction with those on board type AlO3; see paragraph 4-4.

- (2) CIRCUIT OPERATION. The operation of the inverters on this board is explained under Circuit Operation, paragraph 4-4.

- LOW POWER INVERTER (TYPE A123) ASSEMBLY DWG. NO. 4026365

Circuits per board: 4 identical

Current Rating:

Input Current: 6.42 ma

Output Current: 20.6 ma -0.275 + 0.125 volts

- (1) CIRCUIT FUNCTION. The inverters on this board are used in conjunction with those on board type AlO3 (paragraph 4-4). In addition they provide inversion for the write enable signal.

- (2) CIRCUIT OPERATION. The operation of the inverters on this board is explained under Circuit Operation, paragraph 4-4.

- 4-4. TIMING AND CONTROL CIRCUITS

- a. PULSE SHAPER-DELAY LINE DRIVER (TYPE A105) ASSEMBLY DWG. NO. 4026315 Circuits per Board: 5

Circuit.

Major Component

Single Shot

Q(G7), Q(P6)

Inverter

Q(C7)

Delay Line

Emitter Follower

Q(S8)

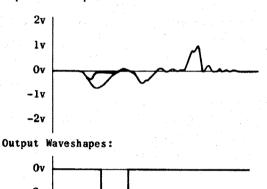

#### Waveshapes:

Input Waveshape:

Output Waveshape:

- (1) CIRCUIT FUNCTION. The delay line driver is triggered by the leading edge of the clock pulse (PTP2M) received from the processor. The driver generates a -10 volt, 800 nanosecond pulse which is applied to the 4 microsecond memory timing delay line.

- (2) CIRCUIT OPERATION. This printed circuit board contains the pulse shaper delay line driver circuits which consist of a single shot multivibrator (SS), a driver-inverter, and an emitter follower. During standby, the single shot is in the clear 0 state. In the 0 state, transistors Q(G7), Q(P6) (NPN, and Q(C7) are nonconducting. Note that the output from the driver transistor, Q(C7), which is applied to the 0.4 microsecond delay line, is at +20 volts.

The PTP2M pulse received from the processor sets the SS. The 1 output from the SS is positive and is direct coupled to the driver transistor. The driver transistor Q(C7) conducts and the driver output goes to near ground potential. Since the 0.4 microsecond delay line is ac coupled to the +20 volt supply and is referenced at ground, a negative 20 volt wave front is presented to the 0.4 microsecond delay line. Since the 0.4 microsecond delay line is open ended, the -20 volt wavefront travels down the delay line and is reflected back. The time required for the wavefront to travel down the delay line and

back again is 0.8 microsecond which determines the width of the output pulse from the pulse shaper circuit. The amplitude of the output pulse is established at -10 volts since the 0.4 microsecond delay line and the 4 microsecond memory timing delay line have the same characteristic impedance and are connected in series. Thus, a -10 volt, 0.8 microsecond pulse is applied to the memory timing delay line.

During the 0.8 microsecond time interval, the SS remains in the set condition. At approximately 0.9 microsecond after the pulse is applied to the memory timing delay line (not shown on the schematic), a timing pulse is coupled from the memory timing delay line to the SS clear side by the emitter follower circuit, Q(S8). The output pulse from the emitter follower clears the SS, and the pulse shaper-driver circuit returns to the standby condition.

b. DELAY LINE BOARDS (TYPES A100, A120 and A121) ASSEMBLY DWG. NO'S. 4026300, 4026360 and 4026361

Circuits per board:

Total delay

| A100- | 32, | 5 <b>0</b> | nanosecond         | LC           | networks |

|-------|-----|------------|--------------------|--------------|----------|

| A120- | 32, | 50         | ${\tt nanosecond}$ | $\mathbf{r}$ | networks |

1.6 microseconds1.6 microseconds

A121- 16, 50 nanosecond LC networks 0.8 microseconds

Current Rating:

Input Current: 1

100 ma -10 volts

Output Current 1 ma -10 volts per tap

Waveshape:

- (1) CIRCUIT FUNCTION. This circuit provides the internal timing and control of the memory, by providing a pulse available at 50 nanosecond intervals from 0 to 4 microseconds.

- (2) CIRCUIT OPERATION. The three delay line sections are connected in series to form one delay line with a total delay of 4.0 microseconds. Taps are available at each 50 nanosecond section. The taps are connected to the

output pins on the board by jumper wires. A preset pattern of jumper wires is connected on each board; this pattern is for nominal times which may require adjustment after the card has been inserted into the memory.

A -10 volt. 800 nanosecond pulse is applied to the delay line input at the beginning of each new memory cycle. As the pulse traverses the delay line, it is delayed by each LC network and is available at the output taps. When utilizing the pulse from the delay line, an emitter follower circuit must be used to couple the pulse to the timing control circuits. The emitter follower prevents excessive loading of the delay line by matching the impedance between the delay line and the timing control circuits.

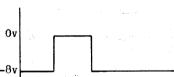

c. EMITTER FOLLOWER and AND GATE (TYPE A127) ASSEMBLY DWG. No. 4026377 Circuits per Board: 6

| Circuit              | major Component   |

|----------------------|-------------------|

| AND Gate             | CR(R9) and CR(S9) |

| OR Emitter Follower  | Q(C7)             |

| Emitter Follower     | Q(Q6)             |

| AND Emitter Follower | Q(L7)             |

| OR Emitter Follower  | Q(E6)             |

| OR Emitter Follower  | Q(J6)             |

|                      |                   |

#### Current Ratings:

# Input Current

- 1 ma 0.3 volts; 0.54 ma -9 volts OR input,

- 2 ma 0.3 volts; 0.67 ma -9 volts 2) AND input,

#### Output Current

Diode leakage current only at -9 volts 6.5 ma  $-0.35 \pm 0.65$  volts

(1) CIRCUIT FUNCTION. - The emitter followers provide impedance matching between the delay line and the low power inverters used in the timing control of the memory. Three of the emitter followers have OR circuits on the inputs to obtain a timing pulse width greater than 0.8 microsecond. One emitter follower has an AND gate on the input to obtain a timing pulse width less than 0.8 microsecond.

The AND gate on this board is a two diode gate with its inputs and output available at the backboard. This circuit is used in the memory wherever negative AND gate logic is required.

(2) CIRCUIT OPERATION. - The emitter follower has a high input impedance, a low output impedance and a voltage gain of less than 1. The emitter follower transistor is biased for continuous conduction. When a negative pulse is applied to the base, the emitter goes negative. When a positive pulse is applied to the base, the emitter goes positive. Thus the emitter follows the base input.

#### 4-5. ADDRESS SECTION CIRCUITS

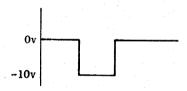

a. SELECTOR SWITCH (TYPE A101) ASSEMBLY DWG. NO. 4026303

SELECTOR SWITCH LOAD (TYPE A102) ASSEMBLY DWG. NO. 4026306

Circuits per Board: A101-3 identical; A102-16 load resistors Current Ratings:

Input current (max): 19 ma -0.15 to -1.5 volts

Output current (max): 385 ma -0.15 to -0.75 volts

## Waveshapes:

Input Waveshapes:

(1) CIRCUIT FUNCTION. - The selector switches are controlled by the address information received from the computer. They select one bus transformer and a group of eight line transformers in the selection system for both the X and Y axis. There are 32 selector switches, in four groups of eight switches, used in the memory. One switch from each group is selected at one

time. When address information is received, the selector switch operates the associated selection system transformer by providing a low impedance path to ground for the read/write drive current. In the unselected state the collector supply of the selector switch transistor provides reverse-bias potential to the diodes of the selection system.

When the storage capacity of the memory is increased, selector switch load cards must be added. The load resistors on the load board are paralleled with the collector load resistors of the selector switches; two load resistor cards are required for each core stack utilized. The resistors on the load card, when paralleled with the collector resistors, maintain a constant RC product of the resistors, and the backboard wiring and selection system capacitance. The backboard wiring and selection system capacitance increases as the storage capacity is increased.

(2) CIRCUIT OPERATION. - The selector switch consists of two transistors. The first transistor, Q(S7), is an emitter follower biased such that saturation of the transistor occurs when a negative signal is received at the input. The transistor is reverse-biased when a positive signal is received at the input. When the transistor is conducting, unselected, the output from the emitter is negative. When the transistor is nonconducting, selected, the output from the emitter is positive. The second stage of the switch is an NPN amplifier-switch. When the output from the first stage is negative, the second stage is reverse-biased, nonconducting, and the output from the switch is at +20 volts. The diode in the base circuit of Q(Q6) clamps the base potential at -0.4 volts, the diode drop. When the output from the first stage is positive. the second stage is forward biased and conducts. In this state, the selected state, transistor Q(Q6) presents a low impedance path to ground for the read/ write current applied to the selection system.

When in the unselected condition, the collector supply of the switch Q(Q6) must supply charging current for the capacitance in the backboard wiring and in the selection system, plus a sufficient potential to reverse-bias the diodes in the unselected transformer circuits. When one stack is used, the collector supply and one load source is sufficient to supply this charging current. However, when more than one stack is used, the collector supply and one load source are not sufficient to charge the capacitance in the required time. Thus an additional current source is necessary. For each stack added, one selector switch load circuit is paralleled with each collector supply.

The load resistors maintain a constant R.C. product consisting of the load resistors, and the backboard and selection system capacitance.

b. TRANSFORMER-DIODE MODULE (TYPE Al18 and Al19) ASSEMBLY DWG. NO. 4026354 AND 4026357 SCHEMATIC DWG. NO. 4026404

Module components: 1 bus transformer; 8 line transformers Component:

T1 Bus Transformers T2-T9 Line Transformers

- (1) CIRCUIT FUNCTION. The transformer-diode modules are used to select the X and Y drive lines of the core stack, and to provide a path for the read/write drive current. Eight modules are used to select the X drive lines and eight are used to select the Y drive lines.

- (2) CIRCUIT OPERATION. Eight transformer-diode modules are mounted on one printed circuit board. One such printed circuit board (type 118) provides the X selection and a second such board (type Al19) provides the Y selection. The inputs to the primary of the bus transformers of all eight modules are connected in parallel; i.e., pin POl of all modules is connected by printed wiring and is available at one of the jack pins of the board; the same is true of PO2. Pin PO4 on each module has a separate connection. The centertap connection on the line transformers are connected in parallel with the corresponding transformer in each module; e.g., pin PO6 of all line transformers is connected in parallel by the printed circuit wiring and is available at a jack pin. One side of the secondary from each line transformer has a separate drive line connection. The other side of the secondary from all line transformers is connected to ground.

The read drive current is applied to pin PO1 of all X bus transformers simultaneously, at the proper time, and the write drive current is applied to pin PO2 of all X but transformers simultaneously, at the proper time. The return path for either the read or write currents is through pin PO4 which is connected to a selector switch circuit. One output from a line transformer is obtained when the selector switch associated with the transformer centertap is operated. The operation of the selector switch applies a low impedance path to ground for the transformer. The read current and write current connections to the Y selection board are the reverse of that for the X selection board.

When read drive current is presented at pin PO1, diode CR1 is forward biased and conducts. The drive current is presented to one half the primary of the bus transformer. The output from the secondary of the bus transformer

is diode coupled to all line transformers associated with the bus transformer. If ground is applied to one line transformer centertap, the read current causes conduction of the coupling diode and the current flows through the primary of that transformer. The output from the line transformer is applied to the associated drive winding of the core stack.

The input diodes to the bus transformer and line transformer primaries serve as isolation diodes. The diodes in the line transformer inputs are reverse biased when the selector switch is unselected. The diodes in the primary of the bus transformer prevent the read current from feeding into the write driver and vice-versa.

#### 4-6. DRIVER CIRCUITS

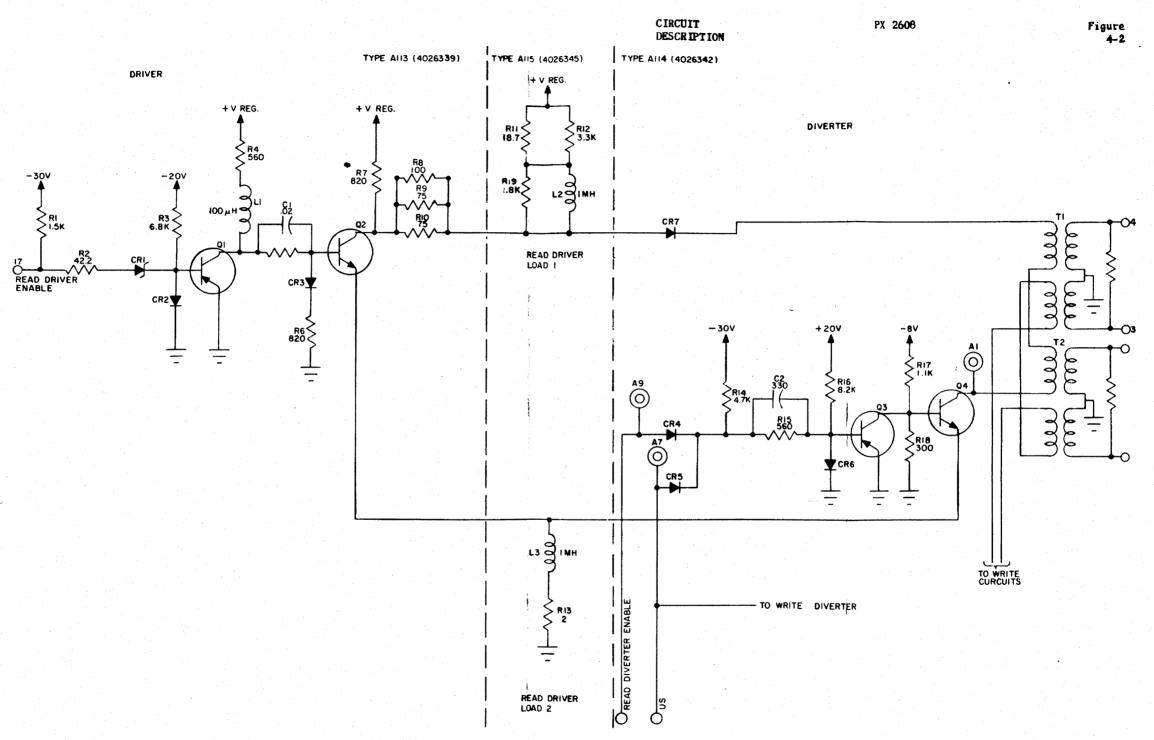

a. READ/WRITE CURRENT PULSE (GENERATOR). - This circuit is packaged on three card types; for a composite schematic refer to figure 4-2.

READ/WRITE DRIVER (TYPE A113) ASSEMBLY DWG. NO. 4026339 READ/WRITE DIVERTER (TYPE A114) ASSEMBLY DWG. NO. 4026342 POWER RESISTOR (TYPE A115) ASSEMBLY DWG. NO. 4026345

## Circuits per Board: 2

| All3<br>Circuit                                                           | Major Component                     |

|---------------------------------------------------------------------------|-------------------------------------|

| Read Driver<br>Write Driver                                               | Q(G7) and Q(L7)<br>Q(E6) and Q(S7)  |

| All4<br>Read Diverter<br>Write Diverter                                   | Q(C7) and Q(Q6)<br>Q(G7( and Q(L7)  |

| All5<br>Circuit                                                           | Major Component                     |

| Read Driver Power Resistor network<br>Write Driver Power Resistor network | L(L3) and L(M8)<br>L(H6) and L(H11) |

# Current Rating, composite circuit:

Input Current: 19.85 ma +0 to -0.6 volts

Output Current: 290 ma nominal vary from 260 ma to 320 ma

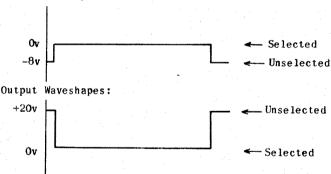

## Waveshapes:

## Input Waveshapes:

the core stack. Each generator supplies both the X and the Y driving currents to one seven-plane core stack.

(2) CIRCUIT OPERATION. - Figure 4-2 is a schematic diagram of the

Write

(2) CIRCUIT OPERATION. - Figure 4-2 is a schematic diagram of the read current pulse generator. When in the standby condition (no current supplied to the core stack), transistors Q1, Q3 and Q4 are nonconducting and Q2 is conducting. With Q2 conducting, the current through L2 and L3 is at maximum.

When a positive pulse is received at the input to Q1, the base-emitter junction is forward-biased and the transistor conducts. The conduction of Q1 applies a negative going pulse from +V regulated to ground to the base of Q2, reverse-biasing the base-emitter junction and the transistor is cut off. The potential across L3 reverses, applying a negative potential to the emitter of Q4. At the same time, the read diverter enable and US signals go positive and forward-bias the base-emitter junction of Q3. Q3 conducts and the base-emitter junction of Q4 is forward-biased and the transistor conducts. The conduction of Q4 diverts the current flowing through L2, to the primary of the output transformers. At the instant of conduction of Q4, the current

Figure 4-2. Read Current Pulse Generator

buildup in L2 provides a positive voltage spike to the primary of the output transformers which serves to bring the current level within the primary winding to maximum, decreasing the rise time of the output current pulse.

The output from the generator stays at a relatively constant level until a negative level is received at the input to Q1. When the input to Q1 goes negative, the base-emitter junction is reverse-biased and the transistor is cut off. The potential across L1 aids in forward-biasing the base-emitter circuit of Q2. Q2 conducts; inductor L2 applies a negative voltage spike to the primary of the output transformers and brings the current level to stand-by level, decreasing the fall time of the output current pulse. The current flow through L3 due to conduction of Q2 is sufficient to apply a positive potential to the emitter of Q4. The read diverter enable and US signals subsides cutting Q4 off, and the generator returns to the standby condition.

The operation of the write current generator is identical to that of the read current generator.

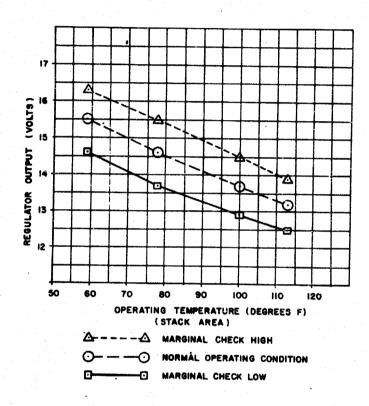

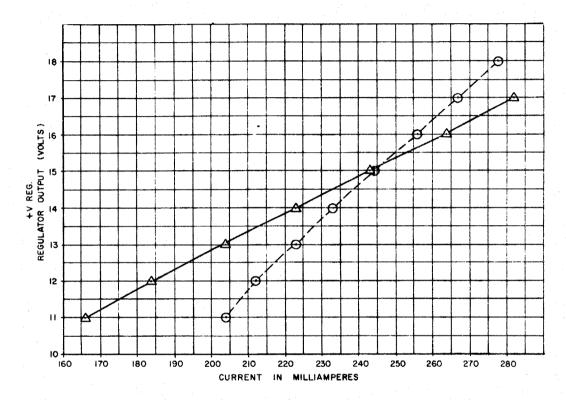

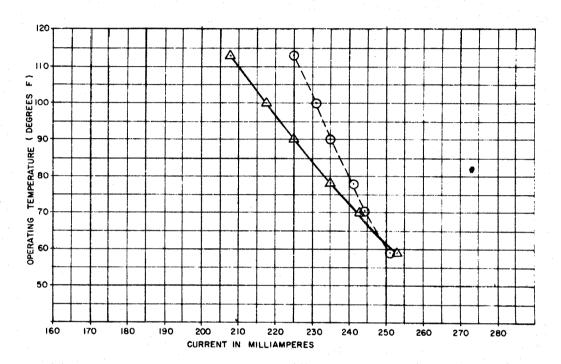

The current output from the generators varies with the (+ V Reg) voltage regulator output which is temperature controlled. Figure 4-3 shows the voltage regulator output vs temperature and current output vs + V Reg.

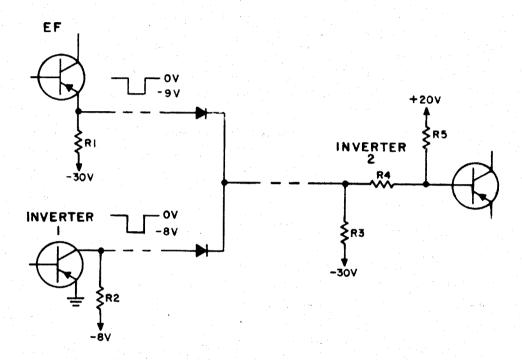

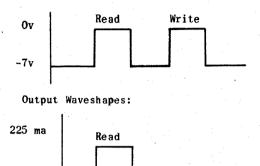

b. INHIBIT DRIVER (TYPE A107) ASSEMBLY DWG, NO. 4026321

Circuits per board: 2 identical

Current Rating:

Output Current: 225 ma

Waveshapes:

Input Waveshapes:

Figure 4-3a. Voltage Regulator Output vs Temperature

O--- INHIBIT DRIVER OUTPUT CURRENT

△---

A READ-WRITE GENERATOR OUTPUT CURRENT

Figure 4-3b. Read/Write and Inhibit Current vs +V Reg

A R/W GENERATOR OUTPUT

O--O INH DRIVER OUTPUT

Figure 4-3c. Read/Write and Inhibit Current vs Temperature

- (1) CIRCUIT FUNCTION. The inhibit driver supplies the current necessary to cancel the effect of the Y write drive current at the core in which a O is to be stored. The driver output is connected to the inhibit line of one core plane within a stack.

- (2) CIRCUIT OPERATION. When the inhibit enable is received on pin 15, the input information pulse is received on pin 14 and the stack select pulse is received on pin 13 of the input AND gate to the inhibit driver; the base of Q(H7) is forward-biased and the transistor conducts. The condition of Q(H7) supplies a forward-biasing current to the base-emitter junction of Q(D7) and this transistor conducts. When Q(D7) conducts, conventional current flows from the +V regulated source through the parallel resistors and capacitor, through the primary of the transformer, through the inhibit winding of the core plane, through the secondary of the transformer, and through the collectoremitter of transistor Q(D7) to the -8 volt source. The primary and secondary of the transformer are connected in series with the inhibit winding. The transformer prevents noise pulses from entering the inhibit line. If a noise pulse is applied to one winding of the transformer it is induced into the second winding, in phase, and the resulting current flow through the inhibit winding due to the noise pulse is reduced to 0.

When any one or all the signals at the input AND circuit go positive, transistor Q(H7) is cut off, and supplies a reverse-biasing potential to the base of Q(D7). Q(D7) is cut off and the inhibit drive current is stopped.

### 4-7. AMPLIFIER CIRCUITS

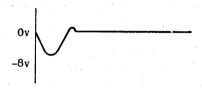

a. PREAMPLIFIER (TYPE A151) DWG. NO. 4026437

Circuits per board: 4

Circuits:

Preamplifier; Class A Q(L7)

Preamplifier; Class A Q(N6)

Preamplifier; Class A Q(S7)

Preamplifier; Class A Q(Q6)

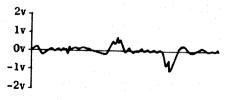

### Waveshapes:

Input Waveshape:

Output Waveshape:

- (1) CIRCUIT FUNCTION. The preamplifier acts as a buffer stage between one sense winding and the associated sense amplifier. The outputs from a maximum of eight preamplifiers, two groups of four preamplifiers, one connected to a core plane from each core stack, can by bussed together and applied to the input to one sense amplifier. Small data signals are amplified, and large noise signals are attenuated by the preamplifier. The common mode noise signals from the sense winding, because of the interwire capacitance between the sense winding and the inhibit winding, are cancelled by the input transformer to the preamplifier.

- amplifier for the data signals received from the sense winding and is biased to clip the bipolar noise signals. When a positive going noise pulse is received at the input to transistor Q(L7), the emitter follows the base positive. The emitter continues to go positive until it reaches the unloaded ac voltage value of the emitter biasing network (approximately 0.7 volt positive). If the input noise continues positive above this value, the transistor is reverse-biased and is cut off. Thus, the output from the pre-amplifier goes from approximately -7 volts during class A standby to approximately -9 volts with a large positive noise signal applied to the input.

When a negative noise pulse is received at the input of the preamplifier transistor, the emitter goes negative. As the emitter goes negative, a negative pulse is RC coupled to and reverse biases diode CR(L2) in the emitter biasing circuit. When the diode is reverse biased to cut off, the emitter current for Q(L7) must be supplied through R(F2) and R(H2) in parallel. Since the parallel resistance of the two resistors is much larger than that of R(J2) and CR(L2) in series, the amplification of the preamplifier transistor is reduced from 1.42 to 0.04. The output from the preamplifier is thus limited when a large negative noise pulse is applied to the input.

b. SENSE AMPLIFIER (TYPE A154) ASSEMBLY DWG, NO. 4026338 SENSE AMPLIFIER LOAD (TYPE A133) ASSEMBLY DWG, NO. 4026399

Circuits per Board: All2 al

| Class A Amplifier | Q(S7) and Q(Q6) |

|-------------------|-----------------|

| Phase Inverter    | Q(L8)           |

| Class C Amplifier | Q(D6)           |

| Class C Amplifier | Q(C7)           |

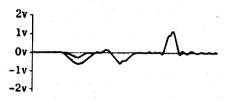

## Waveshapes:

### Input Waveshapes:

- (1) CIRCUIT FUNCTION. The sense amplifier receives the amplified core outputs from one to eight preamplifiers, amplifies the signal, distinguishes between 0's and 1's, stretches the signal to provide for strobing and transfers the information to the processor.

- (2) CIRCUIT OPERATION. The class A amplifier, transistor Q(TU7,8) amplifies the bipolar pulses received from the preamplifier. The output from Q(TU7,8) is transformer coupled to the input of the differential amplifier, Q(F7) and Q(QR7,8). When the input to the class A amplifier goes negative, the transistor conducts more, thereby increasing the voltage drop across the primary of transformer T(R3). This increase in voltage is coupled to the secondary of the transformer appearing positive at pin 3 and negative at pin 6 of the secondary. The positive potential at pin 3 is applied to the base of transistor Q(F7) decreasing the conduction of the transistor. This decrease in conduction decreases the voltage drop across resistor R(C7) and a negative pulse is capacitor coupled C(D4), to the junction of diodes CR(F10) and CR(G10).

The negative pulse forward biases diode CR(G10) and is bypassed to ground by the diode.

The negative potential at pin 6 of transformer T(R3) is applied to the base of transistor Q(QR7,8). The transistor conducts more increasing the voltage drop across R(B10) and a positive pulse is capacitor coupled, C(D9), to the junction of diodes CR(J13) and CR(L13). The positive pulse forward biases diode CR(J13) and is applied to the base of transistor Q(H8) reverse biasing the transistor to cutoff. When the negative strobe pulse is received from the timing and control section on pin 17, the AND gate consisting of CR(Q13) and CR(L9) is satisfied and a negative pulse is available at the output, pin 15.

The output at pin 15, in addition to being available to the processor, is also diode coupled by CR(P6), to the base circuit of feedback amplifier, Q(M8). The negative pulse forward biases the transistor; the transistor conducts and a positive going pulse (from -8 volts to ground) is capacitor coupled to the base circuit of Q(H8). The effect of this feedback pulse is to stretch the output pulse to allow for strobing of the seven sense amplifier outputs. This is necessary due to the variation in circuit parameters.

The input circuit of the class A amplifier is designed to operate with an input load impedance obtained when eight preamplifiers are connected at the input. When only four preamplifiers are used, a load resistor (type Al33) must be connected to input pin 1 of the sense amplifier.

### 4-8. VOLTAGE REGULATION CIRCUITS

a. VOLTAGE REGULATOR (TYPE A116) ASSEMBLY DWG. NO. 4026348

VOLTAGE REGULATOR HEAT SINK (TYPE A117) ASSEMBLY DWG. NO. 4026351

TEMPERATURE CONTROL (TYPE A140) ASSEMBLY DWG. NO. 4026420

Circuits per Board: 1

Voltage Ratings:

Input Voltage: +20 volts unregulated

Output Voltage: Regulated output variable from 13.6 volts to +15.4 volts. See figure 4-3a.

- (1) CIRCUIT FUNCTION. The voltage regulator supplies a temperature compensated voltage to the read/write current pulse generators and to the inhibit drivers. The variable voltage is derived from the +20 volt unregulated dc supply. The output from the circuit is regulated to +1 percent.

- varies inversely with the temperature of the core stack area. This characteristic is obtained by using a temperature sensitive resistor (Sensistor\*) in the feedback circuit of the voltage regulator. As the temperature in the core stack area increases, the resistance of the Sensistor increases and controls the voltage regulator such that the output from the regulator decreases. The Sensistor is physically located on a printed circuit board in the center of the core stack area.

The voltage regulator is a series type voltage regulator utilizing a tetrode transistor, (Q(Pin 17), as the control transistor. A fixed reversebias is developed from the unregulated 20 volt source by inductor L(P4) and is applied to base 2 of Q(Pin 17). The reverse-bias supplies the leakage current for conduction of Q(J5). Since Q(Pin 17) is a tetrode, this leakage current is not amplified by O(Pin 17). Transistors Q(J5) and Q(C7) are DC amplifiers which supply the regulating feedback to base 1 of Q(Pin 17). Since the transistors are biased for conduction at all times, the level of conduction of Q(Pin 17) determines the output from the circuit, while the level of conduction of Q(J5) and Q(C7) determines the level of conduction of Q(Pin 17). diode CR(C3) supplies the reference voltage for dc amplifier Q(C7). The level of conduction of O(C7) determined by the voltage divider network of the Sensistor, and resistors R(B,C2), R(B3) and R(B10), compared with the reference voltage. The level of conduction of Q(J5) is determined by the voltage divider network consisting of R(M2), R(E3), and the collector-emitter voltage drop of Q(C7), and resistor R(ClO). The level of conduction of Q(J5) determines the potential applied to base 1 of O(Pin 17). Switches S1 and S2 control the high, normal, or low output from the regulator. High voltage output is obtained when both switches are open; normal output is obtained when S1 is open and S2 is closed; low output is obtained when both switches are closed.

<sup>\*</sup>A trademark of Texas Instrument Inc.

Resistor R(V6) provides increased regulation under full load conditions by increasing the base-emitter potential of Q(C7) above what it is for low load. Capacitor C(V8) provides filtering of the output. Capacitor C(S7) and resistor R(Q10) provide a path for base current during turn-on of Q(pin 17).

b. SENSE BIAS VOLTAGE REGULATOR (TYPE A153) DWG. NO. 4026442

Circuits per Board: 1

Voltage Ratings:

Input Voltage: -30 volts

Output Voltage: Regulated output variable from -23.5 volts to -24.5 volts.

- (1) CIRCUIT FUNCTION. The sense bias voltage regulator supplies the regulated -24 volts necessary for proper biasing of the sense amplifiers.